Introduction

The Intel ATX specification has been one of the most important specifications since its release in the late 90s’s. Today, Intel gave the green light to show their most recent revision with the biggest update in years. So, we’re going to discuss a few of the changes made.

Change 1 – PCIe 5.0

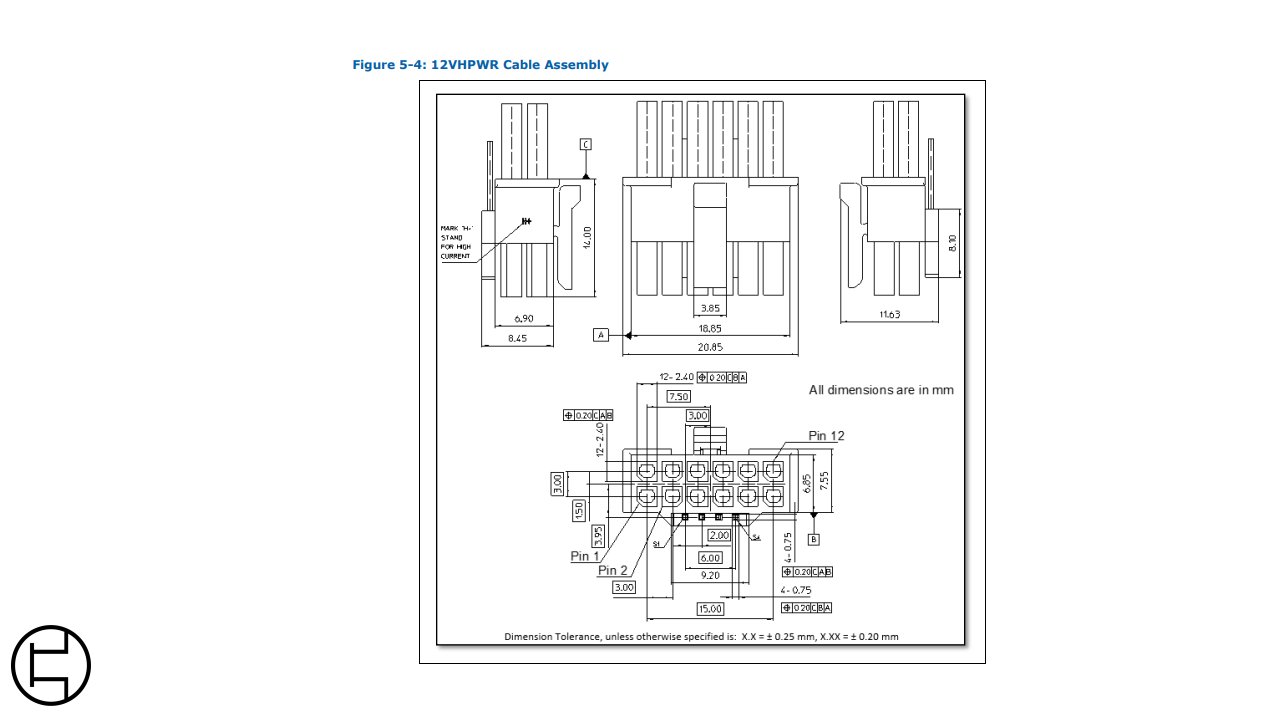

With the last few moves to new PCIe specs, we’ve seen an increased amount of bandwidth per lane. With 5.0 there’s also some major changes coming along regarding power, the main one being the introduction of a new connector. It’s mostly been referred to as the “16 pin” or “12+4 pin” connector, but Intel gives it the official naming of 12VHPWR. There’s also a 48VHPWR connector, but this is only relevant for server/enterprise that were already using 48v as a standard. The new connector is limited to either 150, 300, 450 or 600w of power, with Intel now requiring the connector for any PSU rated at more than 450w. Below an overview of what pins in the +4 part of the connector must be grounded or left open to allow for a certain limit.

| Sense0 | Sense1 | System power up | Sustained power consumption |

|---|---|---|---|

| Ground | Ground | 375 W | 600 W |

| Open | Ground | 225 W | 450 W |

| Ground | Open | 150 W | 300 W |

| Open | Open | 100 W | 150 W |

There is also a higher tolerance for peaks, with the most concerning part being requirements for peak power. In hindsight this might look to be the 200% required limit for 10% duty cycle peaks, but this is a 0.1ms peak, which is not much to worry about. However, my attention eventually came to the 10ms or 25% testing duty cycle requirement of 160%. This would mean that you either have to introduce a “slow” Over Current Protection (OCP) or have it set at a 160% limit. Most modern PSUs have been set between 120-140% and would on paper be unable to handle these kinds of peaks and with that unable to meet ATX 3.0 and PCIe 5.0 compatibility. Below an overview of peak power testing and an example for a 1000w PSU.

| PSU <450w or w/o 12VHPWR connector | PSU >450w and with 12VHPWR connector | Time for Power Excursion (TE) | Testing duty cycle |

|---|---|---|---|

| 100% | 100% | Infinite | --- |

| 110% | 120% | 100 ms | 50% |

| 135% | 160% | 10 ms | 25% |

| 145% | 180% | 1 ms | 20% |

| 150% | 200% | 0.1 ms | 10% |

| Duty Cycle | Time for Power Excursion (TE) | Time Constant (TC) | Power @ TE | Power @ TC |

|---|---|---|---|---|

| 10% | 0.1ms | 0.9 ms | 2000 W | 817 W |

| 20% | 1 ms | 4 ms | 1800 W | 663 W |

| 25% | 10 ms | 30 ms | 1600 W | 693 W |

| 50% | 100 ms | 100 ms | 1200 W | 749 W |

The other two pins are for the GPU itself. These are CARD_PWR_STABLE and CARD_CBL_PRES#. The exact use case of these pins doesn’t seem to be exactly specified in the specification itself, but I personally expect them to be like the 24 pins’ PWR_OK signal.

Change 2 – Looser requirements

With the roughest part out of the way, Intel has also gone the other way around. We went from being allowed within a -5% to 5% range to meet spec to -8% to 5% (12VHPWR) and -7% to 5% (other), allowing a voltage drop down to 11.20 Volts on the 12v rail. There is also the (commonly used) option of having a slightly higher nominal voltage of 12.1 or 12.2 Volts instead of 12 Volts. This both purely applies for the 12v rail, as +5VDC, +3.3VDC, 5VSB and even -12VDC staying the same as older versions. the inclusion of 12VDC is a bit weird, considering this is mostly a legacy thing.

| Output | Range | Minimal | Nominal | Maximum |

|---|---|---|---|---|

| 12VDC | -7% / 5% | 11.2 V | 12 V | 12.6 V |

| 12VDC (PCIe) | -8% / 5% | 11.1 V | 12 V | 12.6 V |

| 5VDC | 5% | 4.75 V | 5 V | 5.25 V |

| 3.3VDC | 5% | 3.14 V | 3.3 V | 3.47 V |

| 5VSB | 5% | 4.75 V | 5 V | 5.25 V |

| -12VDC | 10% | -10.8 V | -12 V | -13.20 V |

I did expect the spec to become tighter over time, considering modern PSUs have been able to keep a much tighter voltage regulation, ripple, and other factors of electrical performance. Instead, the choice was made to make the PSUs tolerate heavier peaks and in return allowing other parts of the spec to be slightly looser.

Change 3 – Other

A few other more minor changes include

A requirement for the PSU to be able to turn on/off 175.200 times per year

A requirement for Over Temperature Protection instead of a recommendation

Changes in low load efficiency, requiring 60% and recommending 70% efficiency at 2% of its rated capacity

Higher expected speed in power on signal to allow for faster system wake time

Efficiency and design requirements for ALPM (Alternative Low Power Modes)

References to Cybenetics as a certification next to 80 plus and Energystar.

Read More

For more information, I recommend reading

The ATX specification itself: ATX_Version_3.0

This article from Aris Mpitziopoulos: https://www.tomshardware.com/news/intel-atx-v3-psu-standard