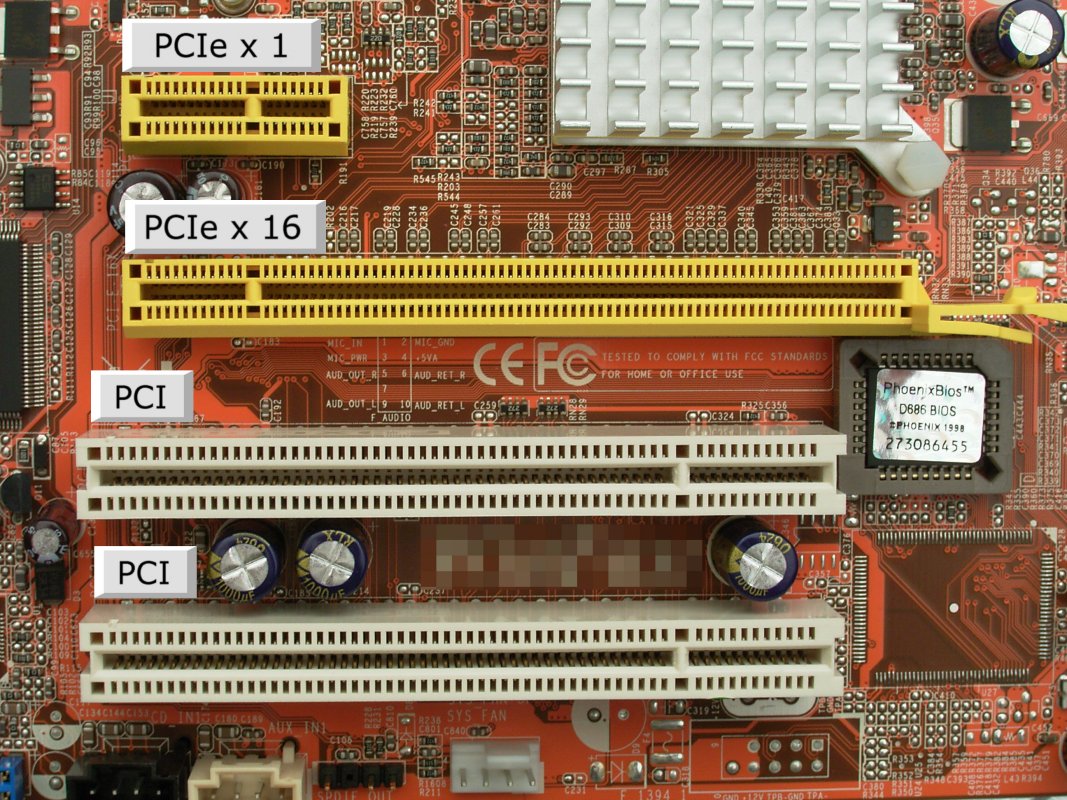

(Image credit: Wikipedia Commons)

PCI SIG, the organization behind the PCIe specifications that govern information for the expansion bus standard, is moving to PCIe 6.0 by the end of this year.

PCI SIG president Al Yanes announced today on a press release, stating that the specification has reached final draft stage, version 0.9. This is the stage where members conduct internal reviews and testing to ensure it meets requirements. PCI SIG is on track to ensure a doubling of data rates while maintaining backward compatibility. Version 0.9 confirms the final specifications and shouldn’t have any major changes expected. It is expected to release in December, assuming the process goes smoothly

The PCIe 6.0 specification features include:

- 64 GT/s data rate and up to 256 GB/s via x16 configuration, doubling the bandwidth of the PCIe 5.0 specification

- PAM-4 (Pulse Amplitude Modulation with 4 levels) encoding and leverages existing 56G PAM-4 in the industry

- FLIT (flow control unit)-based encoding

- Low-latency Forward Error Correction (FEC) with additional mechanisms to improve bandwidth efficiency

- Backward compatibility with all previous generations of PCIe technology

While we may not see any noticeable devices using PCIe 6.0 by the end of the year, do remember that the transition period is a hefty period. Even with the current market, many consumer GPUs do not utilize a full 3.0 or 4.0 x16 bus. With PCIe 5.0 spec being announced a while back, we are yet to see any PCIe 5.0 devices moving mainstream to the market.